服务热线: 0755-83261303

邮箱:ht@htsemi.com

地址:深圳市龙华区大浪街道浪口社区华昌路315号华昌工业园

封装是什么?简述一下发展历程

发表时间:2022-07-01

发表时间:2022-07-01 浏览量: 5280

浏览量: 5280

我国在半导体封装测试领域具有国际先进水平,体量进入世界前三,技术与世界一流水平不存在代差,是集成电路三大环节中发展最好的一个,且发展速度明显高于其他竞争对手。

封装,IC 芯片的最终防护与统整

经过漫长的流程,从设计到制造,终于获得一颗 IC 芯片了。然而一颗芯片相当小且薄,如果不在外施加保护,会被轻易的刮伤损坏。此外,因为芯片的尺寸微小,如果不用一个较大尺寸的外壳,将不易以人工安置在电路板上。因此,本文接下来要针对封装加以描述介绍。

目前常见的封装有两种,一种是电动玩具内常见的,黑色长得像蜈蚣的 DIP 封装,另一为购买盒装 CPU 时常见的 BGA 封装。至于其他的封装法,还有早期 CPU 使用的 PGA(Pin Grid Array;Pin Grid Array)或是 DIP 的改良版 QFP(塑料方形扁平封装)等。因为有太多种封装法,以下将对 DIP 以及 BGA 封装做介绍。

传统封装,历久不衰

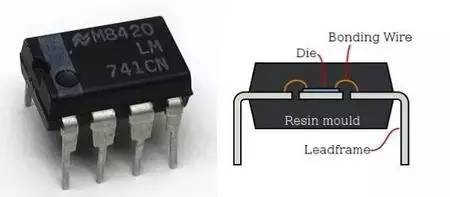

首先要介绍的是双排直立式封装(Dual Inline Package;DIP),从下图可以看到采用此封装的 IC 芯片在双排接脚下,看起来会像条黑色蜈蚣,让人印象深刻,此封装法为最早采用的 IC 封装技术,具有成本低廉的优势,适合小型且不需接太多线的芯片。但是,因为大多采用的是塑料,散热效果较差,无法满足现行高速芯片的要求。因此,使用此 封装的,大多是历久不衰的芯片,如下图中的 OP741,或是对运作速度没那么要求且芯片较小、接孔较少的 IC 芯片。

▲左图的 IC 芯片为 OP741,是常见的电压放大器。右图为它的剖面图,这个封装是以金线将芯片接到金属接脚(Leadframe)(Source :左图 Wikipedia、右图 Wikipedia)

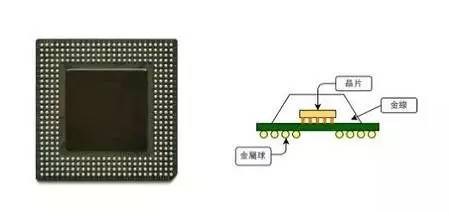

至于球格阵列(Ball Grid Array,BGA)封装,和 DIP 相比封装体积较小,可轻易的放入体积较小的装置中。此外,因为接脚位在芯片下方,和 DIP 相比,可容纳更多的金属接脚相当适合需要较多接点的芯片。然而,采用这种封装法成本较高且连接的方法较复杂,因此大多用在高单价的产品上。

▲左图为采用 BGA 封装的芯片。右图为使用覆晶封装的 BGA 示意图(Source: 左图 Wikipedia)

行动装置兴起,新技术跃上舞台

然而,使用以上这些封装法,会耗费掉相当大的体积。像现在的行动装置、穿戴装置等,需要相当多种元件,如果各个元件都独立封装,组合起来将耗费非常大的 空间,因此目前有两种方法,可满足缩小体积的要求,分别为 SoC(System On Chip)以及 SiP(System In Packet)。

在智慧型手机刚兴 起时,在各大财经杂志上皆可发现 SoC 这个名词,然而 SoC 究竟是什么东西?简单来说,就是将原本不同功能的 IC,整合在一颗芯片中。藉由这个方法,不单可以缩小体积,还可以缩小不同 IC 间的距离,提升芯片的计算速度。至于制作方法,便是在 IC 设计阶段时,将各个不同的 IC 放在一起,再透过先前介绍的设计流程,制作成一张光罩。

然而,SoC 并非只有优点,要设计一颗 SoC 需要相当多的技术配合。IC 芯片各自封装时,各有封装外部保护,且 IC 与 IC 间的距离较远,比较不会发生交互干扰的情形。但是,当将所有 IC 都包装在一起时,就是噩梦的开始。IC 设计厂要从原先的单纯设计 IC,变成了解并整合各个功能的 IC,增加工程师的工作量。此外,也会遇到很多的状况,像是通讯芯片的高频讯号可能会影响其他功能的 IC 等情形。

此外,SoC 还需要获得其他厂商的 IP(intellectual property)授权,才能将别人设计好的元件放到 SoC 中。因为制作 SoC 需要获得整颗 IC 的设计细节,才能做成完整的光罩,这同时也增加了 SoC 的设计成本。或许会有人质疑何不自己设计一颗就好了呢?因为设计各种 IC 需要大量和该 IC 相关的知识,只有像 Apple 这样多金的企业,才有预算能从各知名企业挖角顶尖工程师,以设计一颗全新的 IC,透过合作授权还是比自行研发划算多了。

代替方案,SiP 现身

作为替代方案,SiP 跃上整合芯片的舞台。和 SoC 不同,它是购买各家的 IC,在最后一次封装这些 IC,如此便少了 IP 授权这一步,大幅减少设计成本。此外,因为它们是各自独立的 IC,彼此的干扰程度大幅下降。

▲Apple Watch 采用 SiP 技术将整个电脑架构封装成一颗芯片,不单满足期望的效能还缩小体积,让手表有更多的空间放电池(Source:Apple 官网)

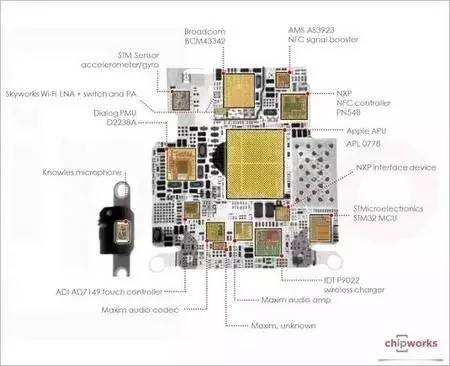

采用 SiP 技术的产品,最着名的非 Apple Watch 莫属。因为 Watch 的内部空间太小,它无法采用传统的技术,SoC 的设计成本又太高,SiP 成了首要之选。藉由 SiP 技术,不单可缩小体积,还可拉近各个 IC 间的距离,成为可行的折衷方案。下图便是 Apple Watch 芯片的结构图,可以看到相当多的 IC 包含在其中。

▲Apple Watch 中采用 SiP 封装的 S1 芯片内部配置图(Source:chipworks)

完成封装后,便要进入测试的阶段,在这个阶段便要确认封装完的IC是否有正常的运作,正确无误之后便可出货给组装厂,做成我们所见的电子产品。至此,半导体产业便完成了整个生产的任务。