服务热线: 0755-83261303

邮箱:ht@htsemi.com

地址:深圳市龙华区大浪街道浪口社区华昌路315号华昌工业园

SMT中,区别于传统的芯片封装有哪些形式?

发表时间:2022-06-27

发表时间:2022-06-27 浏览量: 3971

浏览量: 3971

随着科技的发展,全球的芯片封装工艺正在由双列直插的通孔插装型,逐渐转向金誉半导体今天要讲的表面贴装的封装形式(SMT)。

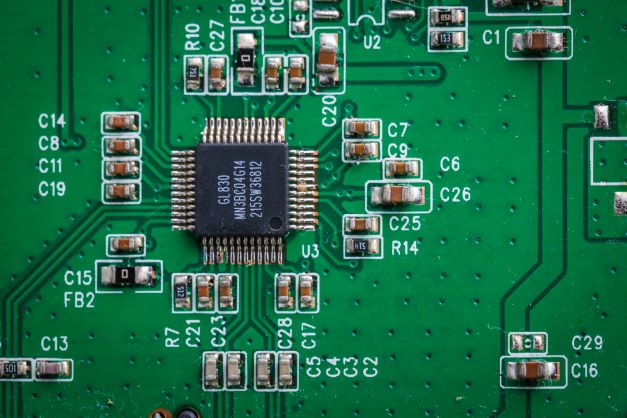

SMT是表⾯贴装技术(表⾯组装技术)(Surface Mounted Technology的缩写),是电⼦组装⾏业⾥最流⾏的⼀种技术和工艺。电⼦电路表⾯组装技术(Surface Mount Technology,SMT),称为表⾯贴装或表⾯安装技术。它是⼀种将无引脚或短引线表⾯组装元器件(简称SMC/SMD,中⽂称⽚状元器件)安装在印制电路板(Printed Circuit Board,PCB)的表⾯或其它基板的表⾯上,通过再流焊或浸焊等⽅法加以焊接组装的电路装连技术。

区别于传统的封装形式,今天要聊的SMT(表⾯贴装技术),对芯片封装难度更大,要求更严,技术更严苛的封装形式,包括晶圆级封装(WLP)、三维封装(3DP)和系统级封装(SiP)三种。

什么是晶圆级封装(WLP)?

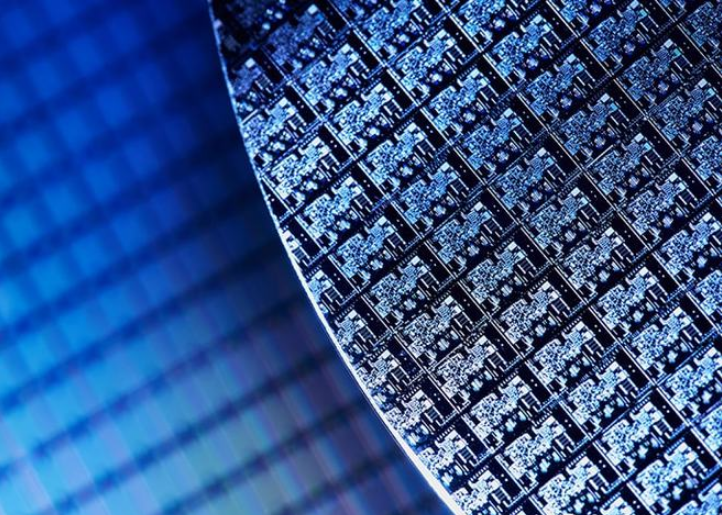

晶圆级封装(Wafer Level Packaging,缩写WLP)是一种先进的封装技术,因其具有尺寸小、电性能优良、散热好、成本低等优势,近年来发展迅速。

不同于传统封装工艺,晶圆级封装是在芯片还在晶圆上的时候就对芯片进行封装,保护层可以黏接在晶圆的顶部或底部,然后连接电路,再将晶圆切成单个芯片。

相比于传统封装,晶圆级封装具有以下优点:

1.封装尺寸小

由于没有引线、键合和塑胶工艺,封装无需向芯片外扩展,使得WLP的封装尺寸几乎等于芯片尺寸。

2.高传输速度

与传统金属引线产品相比,WLP一般有较短的连接线路,在高效能要求如高频下,会有较好的表现。

3.高密度连接

WLP可运用数组式连接,芯片和电路板之间连接不限制于芯片四周,提高单位面积的连接密度。

4.生产周期短

WLP从芯片制造到、封装到成品的整个过程中,中间环节大大减少,生产效率高,周期缩短很多。

5.工艺成本低

WLP是在硅片层面上完成封装测试的,以批量化的生产方式达到成本最小化的目标。WLP的成本取决于每个硅片上合格芯片的数量,芯片设计尺寸减小和硅片尺寸增大的发展趋势使得单个器件封装的成本相应地减少。WLP可充分利用晶圆制造设备,生产设施费用低。

目前,晶圆级封装技术已广泛用于闪速存储器、EEPROM、高速DRAM、SRAM、LCD驱动器、射频器件、逻辑器件、电源/电池管理器件和模拟器件(稳压器、温度传感器、控制器、运算放大器、功率放大器)等领域。

什么是三维封装(3DP)?

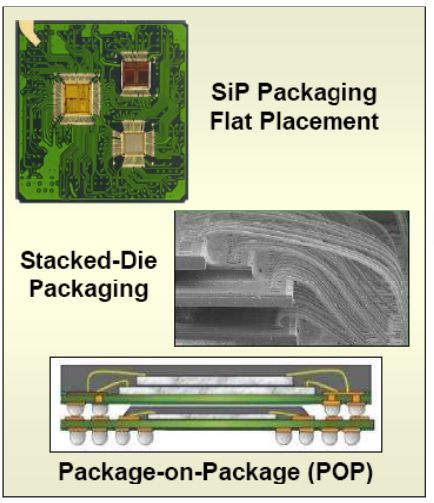

三维封装,英文简称(3DP),包括CIS发射器、MEMS封装、标准器件封装。是指在不改变封装体尺寸的前提下,在同一个封装体内于垂直方向叠放两个以上芯片的封装技术,从而实现大芯片的的功能和性能。它起源于快闪存储器(NOR/NAND)及SDRAM的叠层封装。

主要特点包括:多功能、高效能;大容量高密度,单位体积上的功能及应用成倍提升以及低成本。

什么是系统级封装(SiP)?

系统级封装,将多种功能芯片(包括处理器、存储器等)集成在一个封装内,集成组装成为具有多层器件结构,并且可以提供多种功能的单个标准封装件,形成一个系统或者子系统,以实现更高的性能、功能和处理速度,同时大幅降低电子器件内部的空间要求。即达到所谓的Convergent System的电子系统水平。

系统级封装包含两个非常重要的特征:

(1)将各种不同工艺、不同功能的芯片集成在一个封装内实现强大的系统功能;

(2)将过去PCB版上的分立元件集成在多层集成结构中,使系统小型化,达到所谓的Convergent System 。

封装主要是为了实现芯片内部和外部电路之间的连接和保护作用。这三种较为先进的封装形式各有千秋,应用场合也有所不同,虽目前并未普及,但这一定是未来的发展方向,不久后的将来哪一个会成为最主流的方式,时间会给我们答案。